# Pass-Transistor Adiabatic Logic Using Single Power-Clock Supply

Vojin G. Oklobdžija, Fellow, IEEE, Dragan Maksimović, Member, IEEE, and Fengcheng Lin

Abstract— We present a new pass-transistor adiabatic logic (PAL) that operates from a single power-clock supply and outperforms the previously reported adiabatic logic techniques in terms of its energy use. PAL is a dual-rail logic with relatively low gate complexity: a PAL gate consists of true and complementary NMOS functional blocks, and a pair of cross-coupled PMOS devices. In simulation tests using a standard 1.2  $\mu$  CMOS technology, the circuit has been found to operate up to 160 MHz clock frequency and down to 1.5 V peak-to-peak sinusoidal power-clock supply. Operation of a 1600-stage PAL shift register fabricated in the 1.2  $\mu$  CMOS technology has been experimentally verified.

Index Terms — Adiabatic computing, energy recovery, low power logic.

# I. INTRODUCTION

OW-ENERGY operation is a must in many portable and battery operated systems. Development of adiabatic logic, as an approach to reduce energy consumption of digital logic, has really taken off recently in the works of Athas, Koller and Svensson [1], [4], Younis and Knight [2], Hinman and Schlecht [3], Dickinson, Denker, Avery, Kramer, and Gabara [5]-[8]. The proposed adiabatic logic circuits utilize ac power supplies to recycle the energy used to charge node capacitances in the circuit. Although several interesting approaches have been presented, each encompassing many clever ideas, several weaknesses of these circuits can be identified: the implementation is overly complex [2]; the logic gates are not well suited for CMOS implementation [3]; multiple power-clock supplies are needed for proper stage-to-stage interfacing [4]–[7]; nonadiabatic transitions may compromise the energy savings [8].

In this paper we describe a new *pass-transistor CMOS* adiabatic logic (PAL) that requires only one sinusoidal power-clock supply, has simple implementation, and outperforms the previously published adiabatic logic families [6], [7] in terms of energy consumption.

# II. PAL OPERATION

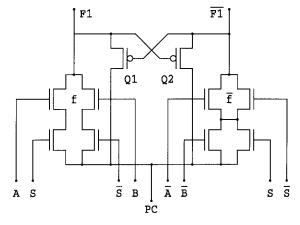

PAL is a dual-rail logic with pass-transistor NMOS functional blocks f and  $\bar{f}$ , and a pair of cross-coupled PMOS devices  $Q_1$ ,  $Q_2$  in each stage, as illustrated by the example of Fig. 1, which performs the 2:1 MUX function:  $F1 = A \cdot S + B \cdot \bar{S}$ . The PAL gate is supplied by a sinusoidal power-

Manuscript received October 3, 1995; revised May 28, 1996. This paper was recommended by Associate Editor S. H. K. Embabi.

Publisher Item Identifier S 1057-7130(97)07486-7.

Fig. 1. 2:1 MUX implemented with PAL.

clock PC. Operation of the gate in Fig. 1 can be summarized as follows: initially PC = 0, and PC starts to raise. Suppose that the inputs A and S are high, making a conducting path from the power-clock PC to the output F1. Given that F1 is connected to PC, F1 will start raising from 0 toward the peak of PC. The node  $\overline{F1}$  will be "tri-state" and kept close to 0 V by the load capacitance of the subsequent gates. As the power clock PC ramps up, the PMOS transistor  $Q_1$  turns on, and the output F1 is charged up to the peak of PC. The transistor  $Q_2$  will stay off. The power clock will then ramp down toward zero, recovering the energy stored on the F1 node capacitance.

The complexity of the logic gate is relatively low, close to that of the style proposed in [7]. The dual-rail nature of the PAL implies that the function f will have to be duplicated as  $\overline{f}$ . However, this will not necessarily result in a 100% duplication because it is possible to "share" transistors in the realization of the NMOS functional blocks f and  $\overline{f}$ .

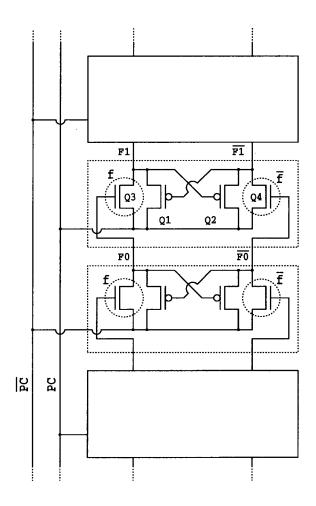

In a chain of PAL gates, the sinusoidal voltage PC supplies all even logic stages, while the inverted (phase-shifted by  $180^{\circ}$ ) sinusoidal voltage  $\overline{PC}$  supplies all odd logic stages. Both PC and  $\overline{PC}$  can be obtained from an efficient single-inductor LC oscillator [5], [8], [9] that can serve as the PAL power supply.

The stage-to-stage interface is illustrated in Fig. 2, where the functional block per stage is a single NMOS pass transistor. Fig. 2 also shows several cycles of the power clocks PC and  $\overline{\text{PC}}$ , logic input F0 and logic output F1, as well as the energy consumption W(t) for a gate supplied by PC. Note how the logic output F1 is delayed with respect to the logic input F0 by one-half of the power-clock period. The chain of PAL gates in Fig. 2 operates as a shift register. The simulation results in Fig. 2 are obtained for the case when a periodic sequence  $\cdots$  1010  $\cdots$  is propagated through the chain. The energy

V. G. Oklobdžija and F. Lin are with the Department of Electrical and Computer Engineering, University of California, Davis, CA 95616 USA.

D. Maksimović is with the Electrical and Computer Engineering Department, University of Colorado, Boulder, CO 80309 USA.

Fig. 2. A chain of simple PAL gates (shift register), and simulation waveforms: power clocks PC and  $\overline{\rm PC}$ ; logic input F0 and logic output F1; energy consumption W(t) per gate. Power-clock frequency is 20 MHz. All device sizes are  $1.8~\mu{\rm m}/1.2~\mu{\rm m}$  in a standard  $1.2~\mu{\rm m}$  CMOS technology.

consumption waveform W(t) shows how the energy is first delivered from the power-clock supply during the part of the clock period when PC is raising, and is then partially recovered during the part of the period when PC is going down. In this example, the energy loss per clock period is 19 fJ per gate.

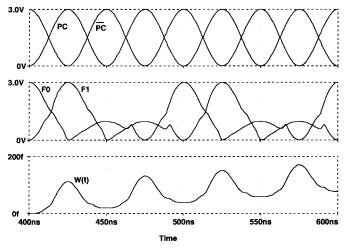

Details of waveforms during one power-clock period are shown in Fig. 3. The logic operation has only two phases: evaluate (E), when the power clock is ramping up, and

Fig. 3. Details of waveforms in the gate of Fig. 2 during one period of the power clock PC.

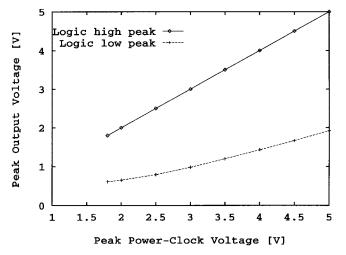

Fig. 4. Peak voltage of a logic high output and a logic low output as functions of the power-clock peak voltage. The simulation results are obtained for the chain of PAL gates shown in Fig. 2 at the power-clock frequency equal to 20 MHz. The device threshold voltages are  $V_{tn}=0.65~{\rm V}$  and  $V_{tp}=-0.85~{\rm V}$ .

discharge (D), when the power clock is going down. The E phase of an odd stage coincides with the D phase of an even stage. Consider the stage with the logic inputs F0 and  $\overline{F0}$  in Fig. 2. Initially, when PC = 0, both output nodes F1 and  $\overline{F1}$  are discharged. During the E phase, when the PC starts ramping up, there is a path through one of the functional blocks because one of the logic inputs (let us assume F0) is

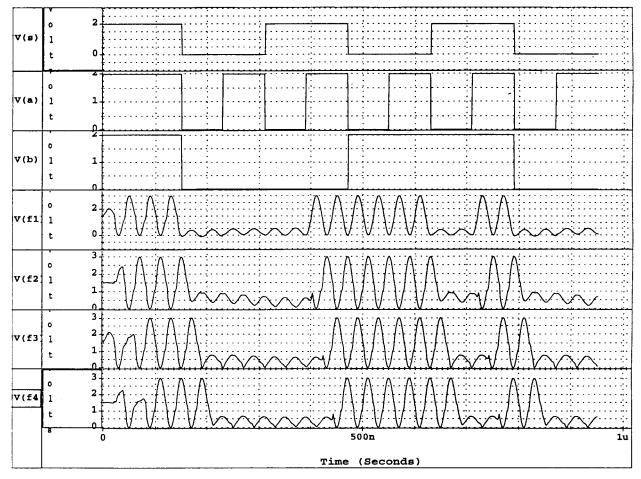

Fig. 5. Simulation waveforms obtained for a chain of 2:1 MUX PAL gates of Fig. 1. All device sizes are the same:  $W/L = 1.8 \ \mu m/1.2 \ \mu m$ .

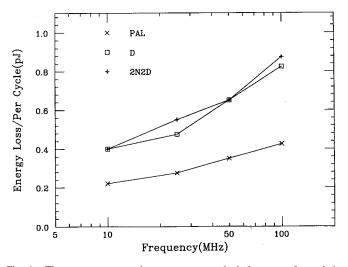

Fig. 6. The energy consumption versus power-clock frequency for a chain of 10 2:1 MUX gates implemented using PAL, the logic proposed by Denker (D) [7], and the 2N2D logic [6]. All device sizes are the same:  $W/L=1.8~\mu \text{m}/1.2~\mu \text{m}$ . The peak power-clock voltage is 3 V.

at the peak of the power clock. Therefore, the output node F1 will begin to ramp up following the power clock PC. Once the voltage difference between F1 and  $\overline{F1}$  increases above  $|V_{tp}|$ , where  $V_{tp}$  is the PMOS threshold voltage,  $Q_1$  turns on and the F1 node capacitance is charged up through  $Q_1$  to the peak of PC. As shown by the current waveforms i(Q3) and i(Q1),

the charge is initially supplied to the output node through Q3 (through the NMOS functional block f), and then by the PMOS device Q1. The other PMOS device Q2 stays off during this clock period because F1 closely follows PC and is always greater than  $\overline{F1}$ . The complementary output  $\overline{F1}$  is tri-stated, and would ideally stay at 0 during the clock period when F1 follows the power clock. However, as shown by the simulation waveforms of Fig. 3,  $\overline{F1}$  does not stay at zero. This is because the device Q4 (the complementary NMOS functional block  $\bar{f}$ ) is conducting during a brief interval at the beginning, and at the end of the PC period, and because of capacitive coupling from the previous stage. Since Q4 is turned off earlier than Q3, and since the charge-up at node  $\overline{F1}$  is not supported by the PMOS device Q2, the peak of  $\overline{F1}$  is significantly lower than the peak of F1. Fig. 4 shows how the peak of the logic high and the logic low outputs depend on the peak of the power-clock supply. The results are obtained by simulation of the chain of PAL gates shown in Fig. 2 at the power-clock frequency equal to 20 MHz. The correct logic levels can be sampled at the peak of the power clock, although the tri-stated output is susceptible to parasitic charge coupling.

During the discharge phase D, the power clock is ramping down. Initially, the discharge of the node F1 is assisted by the PMOS device  $Q_1$ . At the time when PC approaches zero, logic high inputs are close to the peak of  $\overline{\text{PC}}$ , and the final portion of the discharge is done through the conducting functional block.

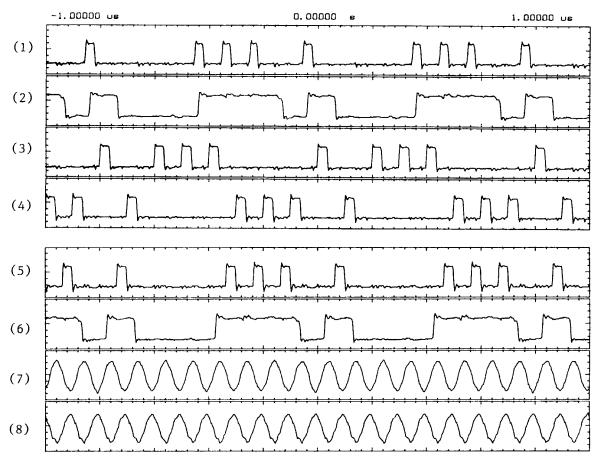

Fig. 7. Experimental waveforms obtained from a 1600-stage PAL shift register fabricated in 1.2  $\mu$  CMOS. Top-to-bottom (5 V/div, 200 ns/div): (1) output #1600; (2) input; (3) output  $\overline{\#3}$ ; (4) output  $\overline{\#3}$ ; (5) output #17; (6) input; (7) power clock  $\overline{PC}$ ; (8) power clock PC. The periodic test sequence is 1101000 ... The sinusoidal 10 MHz power-clocks are 3.6 V peak-to-peak, with 1.8 V dc offset.

Above-threshold logic low inputs help discharge both outputs down to approximately zero volts without excess energy loss.

# III. SIMULATION AND EXPERIMENTAL RESULTS

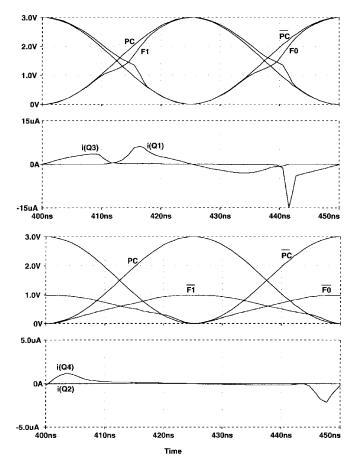

Fig. 5 shows the Spice simulation waveforms obtained for a chain of 2:1 MUX gates of Fig. 1 (extracted from layout), using device models available for a standard 1.2  $\mu$  CMOS technology. Logic inputs to the first gate in the chain are square-wave. In the simulation tests, the circuit has been found to operate up to the power-clock frequency of 160 MHz, and down to 1.5 V peak-to-peak sinusoidal power-clock supply voltage.

A comparison of energy consumption vs. power-clock frequency has been made against the 2N2D logic [6], and the logic proposed in [7]. The results obtained by simulation on the chain of 2:1 MUX gates are shown in Fig. 6. PAL outperforms the other two logic families in this comparison, while operated from a single two-phase power-clock supply.

A 1600-stage PAL shift register, a part of which is shown in Fig. 2, has been fabricated in the 1.2  $\mu$  CMOS technology available through MOSIS. For testing purposes, conventional dc-supplied CMOS buffers were placed between selected PAL outputs and the output pins. Odd stages are supplied by PC, even stages by  $\overline{PC}$ . Fig. 7 shows experimental waveforms

obtained for the power-clock frequency equal to 10 MHz, and a periodic test sequence  $\cdots$  11101000  $\cdots$  passed through the shift register. The sinusoidal power-clocks were 3.6 V peak-to-peak, with 1.8 V dc offset. The conventional buffers are supplied by  $V_{\rm DD}=4$  Vdc, and operate as voltage comparators: the logic high can be observed at an output pin as a pulse centered around the peak of the power-clock waveform. The experimental waveforms verify operation of the PAL shift register. More extensive tests, including power-consumption measurements, are under way.

# IV. CONCLUSION

The pass-transistor adiabatic logic (PAL) circuit described here is a dual-rail logic supplied by a single two-phase AC power clock. The PAL gate complexity is relatively low: a PAL gate consists of true and complementary NMOS functional blocks, and a pair of cross-coupled PMOS devices. In simulation tests using a standard 1.2  $\mu$ m CMOS technology, the circuit has been found to operate up to 160 MHz clock frequency and down to 1.5 V peak-to-peak sinusoidal power-clock supply. It outperforms the previously published adiabatic logic techniques in terms of energy consumption. Operation of a 1600-stage PAL shift register fabricated in the 1.2  $\mu$ m CMOS has been experimentally verified.

### ACKNOWLEDGMENT

The authors would like to acknowledge help received from B. Ackland, A. Dickinson, J. Denker, and T. Gabara from AT&T Bell Laboratories.

# REFERENCES

- [1] J. G. Koller and W. C. Athas, "Adiabatic switching, low energy computing, and physics of storing and erasing information," Proc. PhysComp'92, Dallas, TX, Oct. 2-4, 1992.

- [2] S. G. Younis and T. Knight, "Practical implementation of charge recovering asymptotically zero power CMOS," in Research on Integrated Systems: Proc. 1993 Symposium. Cambridge, MA: MIT Press, 1993, pp. 234–250.

- [3] R. T. Hinman and M. F. Schlecht, "Recovered energy logic—A highly efficient alternative to today's logic circuits," in Proc. IEEE Power Electron. Specialists Conf., 1993.

- W. C. Athas *et al.*, "Low-power digital systems based on adiabatic-switching principle," *IEEE Trans. VLSI Syst.*, vol. 2, Dec. 1994.

- [5] A. G. Dickinson and J. S. Denker, "Adiabatic dynamic logic," *IEEE J.* Solid-State Circuits, vol. 30, pp. 311-314, Mar. 1995.

- [6] A. Kramer, J. S. Denker, S. C. Avery, A. G. Dickinson, and T. R. Wik, "Adiabatic computing with the 2N-2N2D logic family," IEEE Symp. VLSI Circuits/Dig. Tech. Papers, 1994.

- [7] J. S. Denker, "A review of adiabatic computing," in *Proc. 1994 Symp*. Low Power Electron., San Diego, CA, Oct. 10–12, 1994. T. J. Gabara, "Pulsed low power CMOS," Int. J. High Speed Electron.

- Syst., vol. 5, no. 2, 1994.

- [9] D. Maksimović and V. Oklobdžija, "Integrated power clock generators for low-energy logic," IEEE Power Electron. Special. Conf., 1995, pp.

Dragan Maksimović (M'89) was born in Belgrade, Yugoslavia, on July 15, 1961. He received the B.S. and M.S. degrees in electrical engineering from the University of Belgrade, Yugoslavia, and the Ph.D. degree from the California Institute of Technology, Pasadena, in 1984, 1986, and 1989, respectively.

From 1989 to 1992, he was with the University of Belgrade. Since 1992, he has been an Assistant Professor with the Department of Electrical and Computer Engineering, University of Colorado, Boulder. He holds two U.S. patents and has authored

and coauthored more than 40 papers in the area of high-frequency switchmode power conversion. His current research interests include simulation and control techniques in power electronics, soft-switching power converters, and power electronics for low-power, portable systems.

Fengcheng Lin, photograph and biography not available at the time of publication.

Vojin G. Oklobdžija (S'78–M'82–SM'88–F'95) received the M.Sc. and Ph.D. degrees in computer science from the University of California, Los Angeles, in 1982 and 1978, respectively, where he was a Fulbright scholar in 1976. He received Dipl. Ing. (M.Sc.E.E.) degree in electronics and telecommunication from the Electrical Engineering Department, University of Belgrade, Yugoslavia, in

He stayed on the faculty at the University of Belgrade until 1976. Currently he is with

Integration, Berkeley, CA, and the Electrical and Computer Engineering Department of the University of California, Davis, where he came from IBM in 1991. He spent eight years as a Research Staff member of the IBM T. J. Watson Research Center, Yorktown Heights, NY, where he made contributions to development of RISC and super-scalar RISC architecture and holds one of the patents on the IBMRS/6000—"PowerPC" architecture. From 1988 to 1990 he taught courses in computer architecture, computer arithmetic, and computer design at the University of California, Berkeley, as a visiting faculty from IBM. His industrial experience includes positions at the Microelectronics Center of Xerox Corporation, and consulting positions at Sun Microsystems Laboratories, AT&T Bell Laboratories, Siemens, and various others. His interests are in computer design and architecture, VLSI, and fast circuits, and efficient implementations of algorithms and computation. He holds four U.S. and four European patents in the area of circuits and computer design. He has authored and coauthored more than 80 papers in the areas of circuits and technology, computer arithmetic, and computer architecture and given a number of invited talks in the United States, Europe, Latin America, Australia, China, and Japan.

Dr. Oklobdžija is a member of the American Association of University Professors, the New York Academy of Science, and the editorial board of the Journal of VLSI Signal Processing and the IEEE TRANSACTIONS ON VERY LARGE SCALE INTEGRATED (VLSI) SYSTEMS. He is a program committee member of International Solid-State Circuits Conference and a General Co-Chairman of the 1997 Symposium on Computer Arithmetic.